인공지능의 눈부신 발전으로 이미 많은 영역에서 전문가의 역할을 돕거나 심지어 대체하는 경우도 많이 생겼습니다. 이 중에는 각종 엔지니어링 설계도 포함되는데, 어려운 설계 중 하나로 알려져있는 반도체 설계에도 조금씩 사용되는 것 같습니다. 그러나, 아직은 AI만 가지고는 엔지니어를 대체할 수 없는 현황인데, 의외로 기존 방식과 혼합하면 가능할 수도 있다고 합니다. 이번 포스팅에서는 IEEE Spectrum에 소개된 인공지능이 반도체 설계를 돕는 연구내용을 소개합니다.

개요

1971년, 페데리코 파진(Federico Faggin)이 단순한 자와 색연필만을 사용하여 최초의 상업용 마이크로프로세서인 인텔 4004를 설계했을 당시와 비교하면 칩 설계는 비약적으로 발전해왔습니다. 오늘날의 설계자들은 새로운 집적 회로를 계획하고 테스트하기 위해 수많은 소프트웨어 도구를 활용할 수 있습니다. 하지만 칩이 점점 더 복잡해지며 수백억 개의 트랜지스터로 이루어진 설계도 등장하면서, 설계자가 해결해야 할 문제도 더욱 까다로워졌습니다. 그리고 기존의 도구들이 이러한 과제를 완벽히 해결하지 못하는 경우도 종종 발생합니다.

현대 칩 설계는 시스템 사양 정의부터 패키징까지 9단계의 반복적인 과정으로 이루어져 있습니다. 각 단계는 여러 하위 단계로 나뉘며, 문제의 크기와 제약 조건에 따라 몇 주에서 몇 달이 소요될 수 있습니다. 많은 설계 문제는 10¹⁰⁰에서 10¹⁰⁰⁰개의 가능성 중 극소수만이 유효한 솔루션으로 존재하는, 일종의 ‘건초더미에서 바늘 찾기’ 상황과 같습니다. 오늘날 사용되는 자동화 도구는 이처럼 방대한 규모의 실제 문제를 해결하지 못하는 경우가 많아, 결국 사람이 직접 개입해야 하며 이로 인해 과정이 더 번거롭고 시간이 많이 소요됩니다.

이에 따라 칩 설계를 가속화하기 위해 머신러닝을 도입하려는 관심이 커지고 있습니다. 그러나 인텔 AI 연구소의 팀에 따르면, 머신러닝 알고리즘만으로는 특히 여러 제약 조건을 충족해야 하는 문제에서 충분하지 않은 경우가 많았습니다.

예를 들어, 최근 팀이 진행한 설계 작업 중 ‘층 설계(floorplanning)’라는 난제에 AI 기반 솔루션을 적용하려는 시도가 있었습니다. 하지만, 결과적으로는 전통적인 탐색과 같은 비AI 방법을 활용한 도구가 훨씬 성공적이었습니다. 이는 기존의 전통적인 기법을 성급히 배제해서는 안 된다는 것을 시사합니다. 팀은 이제 두 방법의 장점을 결합한 하이브리드 접근법이, 아직 연구가 충분히 이루어지지 않은 분야임에도 불구하고, 가장 유망한 방향이 될 것이라 믿고 있습니다. 그 이유를 설명하겠습니다.

AI 알고리즘의 한계

칩 설계에서 가장 큰 병목 현상 중 하나는 아키텍처가 결정되고 논리 및 회로가 완료된 후 진행되는 물리적 설계 단계에서 발생합니다. 물리적 설계는 칩의 레이아웃과 연결성을 기하학적으로 최적화하는 과정을 포함합니다. 첫 번째 단계는 칩을 CPU 코어, 메모리 블록 등과 같은 상위 기능 블록으로 분할하는 것입니다. 이후 이러한 큰 블록은 매크로(macro)와 표준 셀로 불리는 더 작은 블록으로 나뉩니다. 일반적인 시스템 온 칩(SoC)은 약 100개의 상위 블록으로 구성되며, 각 블록은 수백에서 수천 개의 매크로와 수천에서 수십만 개의 표준 셀로 이루어져 있습니다.

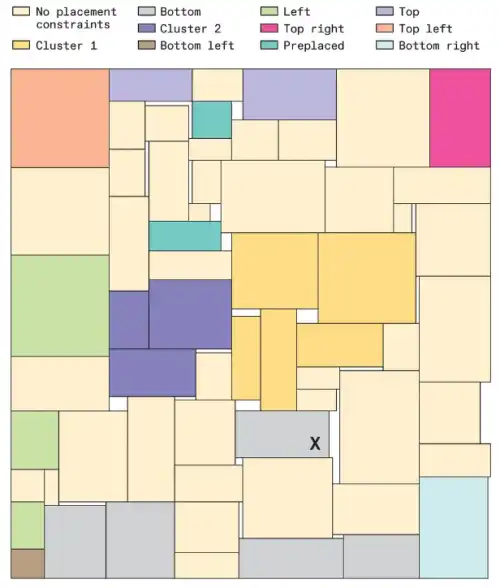

다음 단계는 기능 블록을 고성능, 저전력 소비, 비용 효율성 등의 설계 목표를 충족하도록 배치하는 층 설계입니다. 이러한 목표는 회로 요소를 연결하는 나노와이어의 총 길이(와이어 길이)와 회로가 차지하지 않는 공간(화이트 스페이스)을 최소화함으로써 달성됩니다. 이러한 층 설계 문제는 조합 최적화라는 수학적 프로그래밍 분야에 속합니다. 테트리스를 플레이한 적이 있다면, 단순한 조합 최적화 퍼즐을 다뤄본 셈입니다.

칩 층 설계는 테트리스를 훨씬 복잡하게 확장한 형태와 같습니다. 예를 들어, 일반적인 SoC 층 설계에서 120개의 상위 블록을 배치하는 방법은 약 10²⁵⁰가지로 추정되며, 이는 우주에 존재하는 별의 개수(약 10²⁴개)와 비교해도 압도적으로 많습니다. 매크로와 표준 셀의 배열 가능성은 이보다 몇 배 더 많습니다.

하나의 목표—예를 들어 기능 블록을 가능한 최소한의 실리콘 면적에 배치하는 것—만을 고려한다면 상용 층 설계 도구는 몇 분 안에 이러한 대규모 문제를 해결할 수 있습니다. 그러나 특정 블록의 위치 제약, 모양 제한, 또는 특정 블록 간의 그룹화와 같은 다중 목표와 제약 조건이 주어질 경우 이러한 도구는 제 기능을 하지 못합니다. 이로 인해 설계자는 시행착오와 창의성에 의존해야 하며, 이는 생산 일정에 몇 시간 또는 며칠을 추가할 수 있습니다. 그리고 이는 단지 하나의 하위 단계에 불과합니다.

지난 10년간 머신러닝의 성공에도 불구하고, 칩 설계에는 상대적으로 큰 영향을 미치지 못했습니다. Nvidia와 같은 기업은 하드웨어 설계 프로그램을 위한 스크립트를 작성하고 버그를 분석하기 위해 대규모 언어 모델(LLM)을 훈련하기 시작했습니다. 하지만 이러한 코딩 작업은 층 설계와 같은 복잡한 최적화 문제를 해결하는 것과는 거리가 멉니다.

LLM의 기반인 트랜스포머 모델을 물리적 설계 문제에 적용하고자 하는 유혹이 있을 수 있습니다. 이론적으로 트랜스포머를 훈련시켜 칩의 각 블록의 물리적 좌표를 순차적으로 예측하는 AI 기반 층 설계 도구를 만들 수 있습니다. 하지만 이 경우, 블록이 서로 겹치지 않도록 배치하는 개념을 모델에 가르치는 데 막대한 양의 훈련 데이터와 시간이 필요할 것입니다. 이는 인간에게는 간단한 개념일지라도 컴퓨터가 학습하기에는 매우 까다롭기 때문입니다. 다른 설계 제약 사항, 예를 들어 특정 블록을 가장자리에 배치해야 한다는 요구사항이나 특정 전압원을 공유하는 블록 간의 그룹화와 같은 조건도 마찬가지입니다.

이러한 문제를 해결하기 위해 팀은 새로운 접근 방식을 시도했습니다. 먼저, 블록의 위치를 층 설계에서 효과적으로 전달하기 위한 데이터 구조를 선택했습니다. 그 결과, B*-트리라는 구조를 채택하게 되었습니다. 이 구조에서 각 블록은 이진 트리의 노드로 나타납니다. 층 설계의 왼쪽 아래 코너에 있는 블록이 루트가 되며, 오른쪽 블록은 한 갈래, 위쪽 블록은 다른 갈래가 됩니다. 이러한 패턴은 새 노드마다 계속 반복됩니다. 따라서 트리가 성장하면서 오른쪽과 위쪽으로 퍼지며 층 설계를 캡슐화합니다.

B*-트리 구조의 주요 장점은 블록 위치가 절대값이 아니라 상대적으로 표현되기 때문에 겹치지 않는 층 설계가 보장된다는 점입니다. 예를 들어, “이 위치”가 아니라 “다른 블록 위쪽”과 같은 방식으로 표현됩니다. 따라서 AI 기반 층 설계 도구는 각 블록의 정확한 좌표를 예측할 필요가 없으며, 대신 블록의 크기와 이웃 노드의 크기 및 좌표를 기반으로 좌표를 쉽게 계산할 수 있습니다. 이로써 겹침 문제가 발생하지 않습니다.

이 데이터 구조를 바탕으로 팀은 그래프 신경망, 확산 모델, 트랜스포머 기반 모델 등 여러 머신러닝 모델을 수백만 개의 최적 층 설계 데이터셋으로 훈련시켰습니다. 이 모델은 최적의 블록을 예측하여 이전 블록의 오른쪽 또는 위쪽에 배치하도록 학습했습니다. 하지만 팀은 곧 이러한 단계별 방법이 효과적이지 않다는 것을 깨달았습니다. 약 100개의 블록에 대해 층 설계 문제를 확장하고 겹침 방지 규칙 외에도 블록을 특정 위치에 배치하거나 그룹화해야 하는 강력한 제약 조건을 추가했을 때, AI 모델은 비효율적인 솔루션을 탐색하는 데 시간을 낭비했습니다.

모델의 한계는 이전의 잘못된 배치를 수정할 수 없는 점에 있다고 결론지었습니다. 블록을 순차적으로 배치하기 때문에 회귀적으로 수정하는 것이 불가능했습니다. 강화학습 에이전트를 활용하여 이를 극복할 수는 있었지만, 좋은 모델을 훈련하는 데 필요한 탐색량은 비현실적이었습니다. 이러한 한계에 직면하여, 팀은 블록별 의사 결정을 포기하고 새로운 접근 방식을 모색하기로 했습니다.

칩 설계의 전통으로 돌아가다

대규모 조합 최적화 문제를 해결하는 일반적인 방법 중 하나는 시뮬레이션된 어닐링(Simulated Annealing, SA)이라는 탐색 기법입니다. 1983년에 처음 소개된 SA는 금속 공학에서 영감을 받은 기법으로, 어닐링은 금속을 고온으로 가열한 후 천천히 냉각시키는 과정을 말합니다. 에너지를 점진적으로 감소시키는 이 과정은 금속의 원자가 질서 있게 배열되도록 하여, 급격히 냉각했을 때보다 더 강하고 유연한 소재를 만들 수 있습니다. 이와 유사하게, SA는 모든 가능성을 일일이 확인하지 않고도 최적화 문제의 최적 해법에 점진적으로 근접합니다.

SA의 작동 원리는 다음과 같습니다. 알고리즘은 먼저 무작위로 생성된 해답, 즉 여기서는 B*-트리로 표현된 임의의 층 설계를 생성합니다. 그런 다음 알고리즘은 세 가지 행동 중 하나를 무작위로 수행합니다. 블록 두 개를 교체하거나, 블록을 한 위치에서 다른 위치로 이동시키거나, 블록의 가로세로 비율(면적은 동일)을 조정합니다. 이렇게 생성된 층 설계의 품질은 총 면적과 와이어 길이의 가중 평균값으로 평가되며, 이 값은 해당 행동의 “비용”을 나타냅니다.

새로운 층 설계가 더 나아졌다면(즉, 비용이 줄었다면) 이를 수용합니다. 반대로 비용이 증가했더라도 초기에는 이를 수용합니다. 이는 “나쁜” 결정이 좋은 방향으로 이어질 수 있기 때문입니다. 그러나 시간이 지나면서 알고리즘이 블록을 무작위로 조정할수록 비용이 증가하는 행동은 점점 더 드물게 수용됩니다. 금속 공학에서 금속을 너무 빨리 냉각시키면 원자가 무질서하게 배열될 수 있는 것처럼, 알고리즘의 탐색을 너무 빨리 제한하면 지역 최솟값(local minima)이라고 불리는 최적화되지 않은 해법에 갇힐 위험이 있습니다. 알고리즘에 충분한 탐색의 여유를 주어 이러한 함정을 피하도록 한 후, 원하는 해법(전역 최솟값 또는 그에 가까운 해법)으로 유도할 수 있습니다.

SA는 머신러닝 모델보다 층 설계 문제를 해결하는 데 훨씬 더 성공적이었습니다. SA 알고리즘은 배치 순서를 고려하지 않기 때문에, 언제든지 어떤 블록이라도 변경할 수 있어 초기 실수를 수정할 수 있습니다. 제약 조건이 없을 경우, SA는 수백 개의 블록으로 이루어진 고도로 복잡한 층 설계도 몇 분 안에 해결할 수 있었습니다. 반면, 상용 도구를 사용하는 칩 설계자는 동일한 문제를 해결하는 데 몇 시간이 필요합니다.

제약 조건을 고려한 시뮬레이션된 어닐링

물론, 실제 설계 문제에는 다양한 제약 조건이 존재합니다. 이에 따라 기존 머신러닝 모델에 적용했던 제약 조건(특정 블록 배치 및 그룹화 제한)을 SA 알고리즘에도 적용해 보았습니다. 우선, 층 설계에서 제약 조건을 위반한 횟수를 비용 함수에 추가하여 이를 해결하려고 했습니다. 알고리즘이 제약 조건 위반을 증가시키는 행동을 할 경우, 이를 점점 더 높은 확률로 거부하여 제약 조건을 피하도록 유도했습니다.

하지만, 이 접근법은 오히려 역효과를 냈습니다. 비용 함수에 제약 조건을 포함하면, 알고리즘은 제약 조건을 만족시키는 것과 면적 및 와이어 길이를 최적화하는 것 사이에서 균형을 찾으려 했습니다. 그러나 제약 조건은 타협이 불가능한 요소입니다. 제약 조건 변수의 가중치를 높여 이러한 강성을 반영하려 했을 때, 알고리즘은 최적화를 제대로 수행하지 못했습니다. 위반 사항을 수정하려는 알고리즘의 노력은 전역 최솟값(최적 설계)으로 이어지기보다는, 반복적으로 지역 최솟값(비최적 설계)에 갇히는 결과를 낳았습니다.

머신러닝과의 결합

새로운 접근 방식으로 제약 조건 인지 시뮬레이션된 어닐링(Constraints-Aware Simulated Annealing, CA-SA)을 개발했습니다. 이 변형 알고리즘은 두 개의 모듈로 구성됩니다. 첫 번째는 SA 모듈로, 면적 및 와이어 길이 최적화에 집중합니다. 두 번째 모듈은 무작위로 제약 조건 위반을 선택하고 이를 수정합니다. 이 수정 모듈은 약 10,000번의 행동 중 한 번 정도만 작동하지만, 작동할 때는 면적 및 와이어 길이에 관계없이 항상 결정을 수용합니다. 이렇게 하면 CA-SA 알고리즘이 제약 조건을 만족시키는 해법으로 유도되면서도 최적화 작업을 방해하지 않게 됩니다.

이를 기반으로 다중 CA-SA 반복 실행을 지원하는 오픈 소스 층 설계 도구인 Parsac을 개발했습니다. 인간 설계자는 Parsac의 솔루션 중 최적의 결과를 선택할 수 있습니다. Parsac을 300개 블록까지 포함된 대표적인 층 설계 벤치마크에서 테스트한 결과, 기존 SA 기반 알고리즘 및 머신러닝 모델을 포함한 모든 다른 솔루션을 능가했습니다.

현대 SoC 설계를 반영하지 못하는 20년 이상 된 벤치마크의 한계를 보완하기 위해, 팀은 자체적으로 제약 조건을 추가하여 테스트했습니다. 상업적으로 규모가 큰 문제(약 100개 블록)를 대상으로 한 테스트에서 Parsac은 15분 이내에 성공적으로 문제를 해결하며, 이 부문에서 가장 빠른 층 설계 도구로 자리 잡았습니다.

향후 전망

SA 기반 층 설계를 더욱 개선하기 위해 머신러닝 모델과의 협력을 고려하고 있습니다. 예를 들어, SA가 생성한 층 설계를 기반으로 AI 모델이 설계 품질을 개선할 수 있는 행동을 예측하도록 훈련할 수 있습니다. 그런 다음 이 모델을 CA-SA 알고리즘의 의사 결정에 활용하여 무작위 행동뿐만 아니라 모델이 제안한 “스마트”한 행동도 수용하도록 설정할 수 있습니다. 이렇게 하면 알고리즘이 최적 해법을 찾기 위해 수행하는 행동의 수를 대폭 줄이고 실행 시간을 단축할 수 있습니다. 그러나 무작위 행동을 허용하는 것도 여전히 중요합니다. 그렇지 않으면 알고리즘이 최적화되지 않은 함정에 빠질 위험이 있기 때문입니다.

이와 같은 접근법은 층 설계뿐만 아니라 칩 설계 내의 다른 복잡한 조합 최적화 문제를 해결하는 데에도 유용할 수 있습니다. 예를 들어, 코어 내 인터커넥트 라우팅 최적화나 게이트 및 입력 수를 최소화하여 회로를 구성하는 부울 회로 최소화 문제 등이 해당됩니다. 현재 팀은 기하학적 탐색에 기반한 또 다른 비AI 기술을 개발하여 불규칙한 블록이 포함된 층 설계를 처리하고 있습니다. 초기 결과에 따르면 이 새로운 접근 방식은 Parsac보다 더 빠를 가능성이 있지만, 되돌릴 수 없는 문제로 인해 해결책이 최적화되지 않을 수 있습니다.

또한, Parsac을 매크로 배치(층 설계보다 더 세밀한 단계)로 확장하려 하고 있습니다. 이는 수백 개에서 수천 개의 요소로 스케일을 확장하면서도 제약 조건을 준수해야 하는 문제입니다. 이 경우, CA-SA 단독으로는 문제를 효율적으로 해결하기에 너무 느릴 수 있어 머신러닝이 중요한 역할을 할 것으로 기대됩니다.

새로운 벤치마크의 필요성

Parsac 개발 경험은 새로운 벤치마크를 마련할 필요성을 일깨워 주었으며, 이를 기반으로 샘플 층 설계의 오픈 데이터셋을 제작하게 되었습니다. 이러한 현대적 벤치마크는 새로운 칩 설계 도구를 검증하려는 연구자들에게 점점 더 긴급한 요구로 자리 잡고 있습니다. 최근 연구에서는 기존 벤치마크나 독점 설계를 기반으로 새로운 머신러닝 알고리즘의 성능을 주장하고 있지만, 이러한 주장들의 신뢰성에 의문이 제기되고 있습니다.

이를 해결하기 위해 GitHub에 공개한 두 가지 데이터셋, FloorSet-Lite와 FloorSet-Prime을 제작했습니다. 각 데이터셋에는 머신러닝 모델 학습을 위한 100만 개의 설계와, 면적과 와이어 길이를 최적화한 100개의 테스트 설계가 포함되어 있습니다. 이 설계들은 현대 SoC 층 설계의 폭넓은 복잡성을 포착하도록 설계되었으며, 20개에서 120개 블록으로 구성되어 실용적인 설계 제약 조건도 포함하고 있습니다.

이 두 데이터셋은 복잡성에서 차이를 보입니다. FloorSet-Lite는 직사각형 블록을 사용하여 설계 초기 단계의 단순한 형태를 반영합니다. 반면, FloorSet-Prime은 설계가 진행되면서 매크로, 표준 셀, 기타 구성 요소의 배치가 세밀하게 조정되어 발생하는 비정형 블록을 포함합니다. 이 비정형 블록은 설계 후반 단계에서 더 흔히 나타나는 요소입니다.

비록 이러한 데이터셋은 인공적으로 생성된 것이지만, 상용 칩의 특성을 충실히 반영하기 위해 세심한 노력을 기울였습니다. 이를 위해 블록의 크기, 제약 조건의 유형 등 층 설계 속성에 대한 통계 분포를 상세히 분석하고, 이를 기반으로 샘플링하여 실제 칩 설계와 유사한 합성 층 설계를 제작했습니다.

머신러닝과 하이브리드 알고리즘의 미래

이처럼 강력하고 공개된 데이터셋은 칩 설계에서 머신러닝의 활용을 크게 촉진할 수 있습니다. 그러나 층 설계와 같은 복잡한 최적화 문제에서 완전히 AI 기반의 솔루션이 등장할 가능성은 낮아 보입니다. 딥러닝 모델은 객체 인식이나 언어 생성과 같은 작업에서 뛰어난 성과를 보여주지만, 이는 통계적 규칙성을 학습 데이터에서 포착하고 이를 원하는 출력과 연관 짓는 데 탁월하기 때문입니다. 하지만 이는 조합 최적화와 같은 어려운 문제를 해결하는 데 적합하지 않습니다. 이러한 문제는 단순한 패턴 인식을 넘어선 기술이 필요합니다.

대신, 하이브리드 알고리즘이 궁극적인 승자가 될 것으로 예상됩니다. AI 모델이 가장 유망한 탐색 경로를 식별하는 법을 학습함으로써 Parsac과 같은 탐색 알고리즘을 지능적으로 안내할 수 있습니다. 이를 통해 칩 설계자는 문제를 더 빠르게 해결할 수 있으며, 더 복잡하고 전력 효율이 높은 칩을 설계할 수 있게 됩니다. 나아가 설계의 여러 단계를 하나의 최적화 문제로 통합하거나, 여러 설계를 동시에 진행할 수도 있을 것입니다.

AI가 칩을 완전히 설계하거나 단일 설계 단계 전체를 독립적으로 해결할 수는 없을지 모릅니다. 그러나 혁신적인 접근 방식과 결합된다면, AI는 칩 설계 분야에서 게임 체인저가 될 것입니다.

마무리

이번 포스팅에서는 현대 칩 설계에서의 주요 도전 과제와 이를 해결하기 위한 새로운 접근 방식을 살펴보았습니다. 특히, 기존의 시뮬레이션된 어닐링(SA) 기법에 제약 조건 인지 기능을 추가한 CA-SA 알고리즘과 이를 활용한 Parsac 도구의 가능성을 논의하며, 이러한 하이브리드 접근 방식이 칩 설계 분야에서 가져올 변화에 대해 전망했습니다. 또한, 머신러닝과 전통적인 최적화 기법의 결합이 복잡한 설계 문제 해결의 열쇠가 될 수 있음을 강조하며, 이를 위한 새로운 벤치마크 데이터셋의 중요성도 다루었습니다. 앞으로도 이런 혁신적인 기술들이 칩 설계 프로세스를 더욱 효율적이고 정교하게 발전시키길 기대합니다.